## BACHELOR OF TECHNOLOGY (C.B.C.S.) (2020 COURSE) B.Tech.Sem - IV E&C :SUMMER- 2022 SUBJECT : DIGITAL COMMUNICATION

Day: Tuesday Time: 10:00 AM-01:00 PM Date: 14-06-2022 S-24601-2022 Max. Marks: 60 N.B.: 1) All questions are **COMPULSORY**. 2) Figures to the right indicate FULL marks. 3) Draw diagrams wherever necessary. 4) Use of Scientific Calculator is allowed Q.1 What is the meaning of sampling? Explain in detail types of sampling with (10) suitable diagram and waveforms. OR Q.1 a) Differentiate PAM, PWM and PPM. (05)b) Explain PWM transmitter with suitable block diagram and waveform. (05)Q.2 Explain in detail delta modulation transmitter and receiver with suitable block (10) diagram and mathematical expressions. OR A compact CD disc records the audio signal using PCM. Assume Audio signal (06) Q.2 a) of 10KHz. Calculate i) Nyquist rate fs If Nyquist samples are quantized into 17000 levels. Identify the no. of binary digits to encode a sample Signalling rate (Bit date) iii) (04)b) Discuss the different noise effects in detail Find error probability of coherent FSK when amplitude of input at coherent (10) Q.3 optimal receiver is 10mv and frequency 1MHz the signal corrupted with white noise of PSD 10<sup>-9</sup> W/Hz. The data rate is 100 kbps. [ erfc(1.01)=0.1531, erfc(1.11)=0.1164, erfc(1.22)=0.0844 and erfc(1.33)= 0.0599 ] OR Draw and explain the block diagram of BPSK modulator with suitable (10) Q.3 mathematical expressions in detail. Explain the working principal of scrambling and unscrambling (Descrambling) (10) **Q.4** with neat diagram.

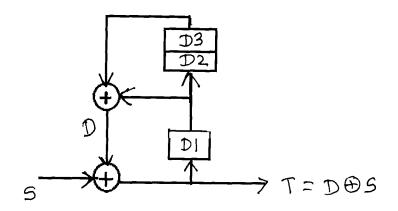

Q.4 Design the corresponding scrambles. If a sequence S=1010101000111 is (10) applied to the input of this scrambler, determine the output sequence T.

Q.5 Explain error probability of BPSK. (10)

OR

- Q.5 Explain the properties of matched filter. (10)

- Q.6 Explain FHSS transmitter and receiver in detail with neat diagram (10)

OR

Q.6 A spread spectrum communication system has the following parameters. (10) Information bit duration, Tb = 4.095ms, PN chip duration, Tc = 1µs. Find the processing gain. What is the number of shift register required? Also find the jamming margin if Eb/No = 10 for BPSK scheme.

\* \* \* \* \*